RISC-V CPU

Project Information

RISC-V 32I CPU designed as part of the instruction set architecture (ISA) module for 2nd year EIE at Imperial College London.

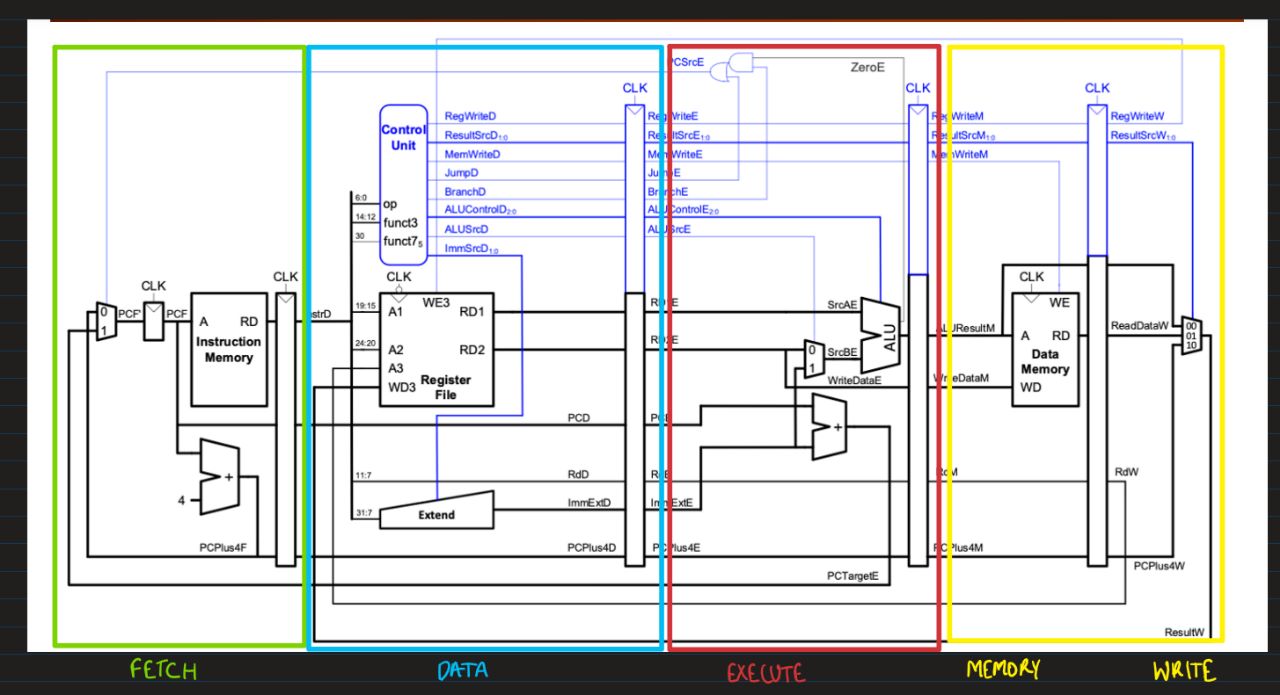

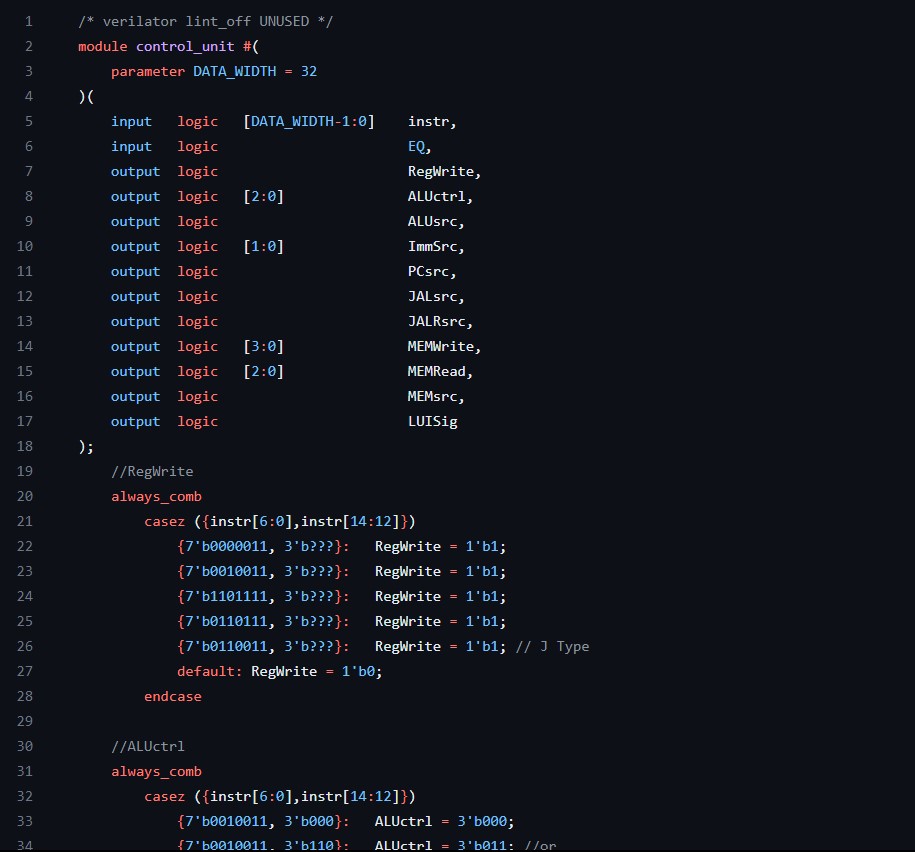

The multi-stage pipe-lined CPU compliant to RISC-V 32-bit integer instruction set architecture was developed in SystemVerilog.

We built both pipelined and data cached version of the CPU as well as included an independent C++ test-bench which can be

used to assert the functional correctness of any given CPU. GitHub automation was used to ensure version check on different branches

and prevent breaking of main branch.